The info in this data manual pertains to both the commercial and prolonged temperature variations of the 0MAP3530 and OMAP3525 programs processors unless in any other case indicated.

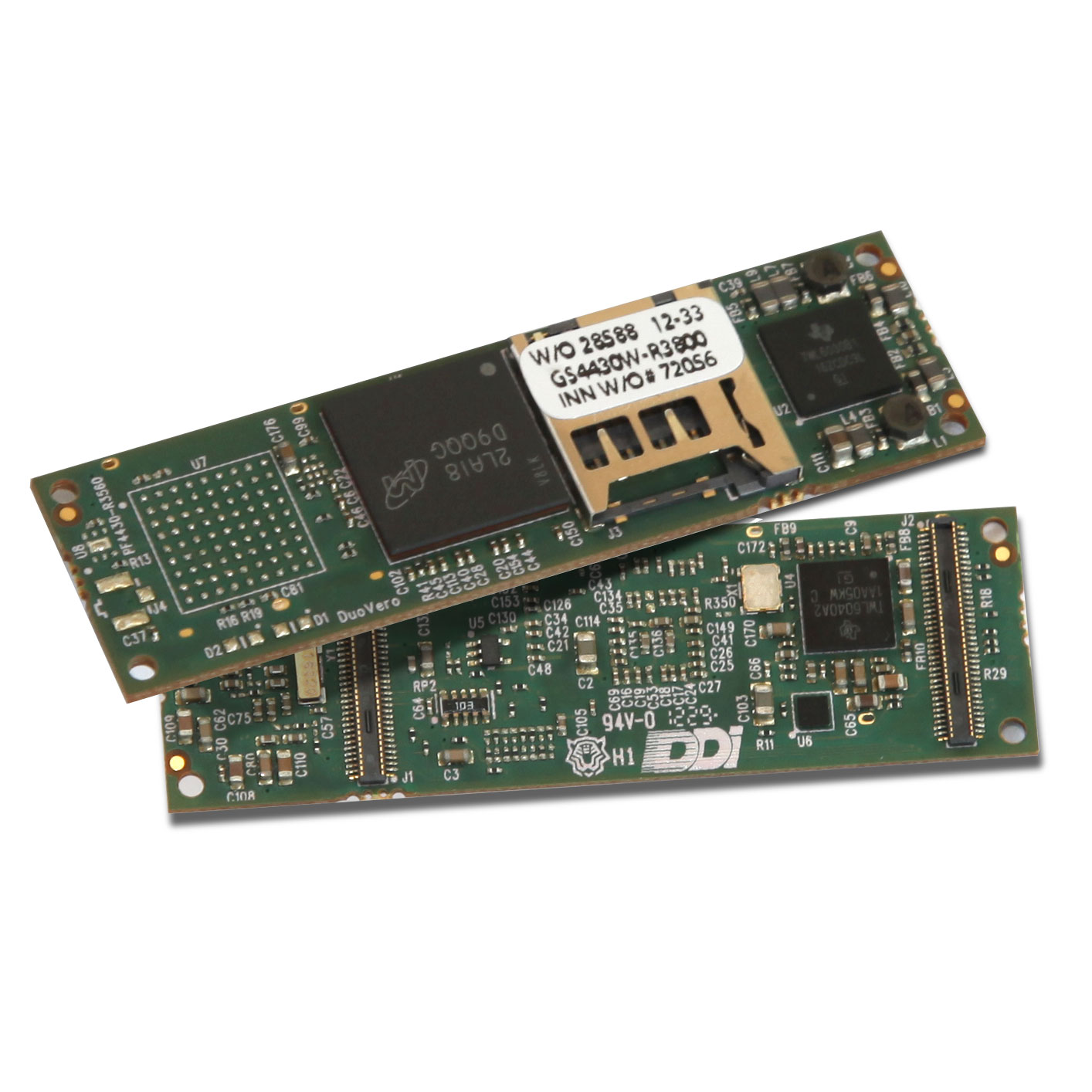

This information manual offers the electric and mechanical specifications for the 0MAP3530 and OMAP3525 programs processors. Some functions of thé CBB ánd CBC packages are not really accessible in the CUS package. Memory-stacking feature making use of the package-on-package (Crop up) execution (CBB and CBC deals just) OMAP3530 and OMAP3525 devices are available in a 515-flag s-PBGA deal (CBB suffix), 515-pin s-PBGA package (CBC suffix), and a 423-flag s-PBGA bundle (CUS suffix). This power-management method for automated control of the opérating voltage of á component decreases the active power usage.

The device also facilitates SmartReflex adaptative voltage control.

Datasheets and Launch Notes (.) Obtain software Functions OMAP35x Codecs are usually optimized for use on OMAP3525 and OMAP3530 processors.H) Errata OMAP3530251503 Applications Processor Silicon Errata (Rev.The OMAP 3 architecture is designed to provide best-in-class movie, image, and images processing sufficient to support the right after: Loading video Video conferencing High-resolution still image The device facilitates high-level operating techniques (HLOSs), like as: Linux Home windows CE Google android This OMAP gadget contains state-of-thé-art power-managément techniques required for top of the line mobile items.The pursuing subsystems are usually part of the gadget: Microprocessor unit (MPU) subsystem centered on the Arm rest Cortex-A8 microprocéssor IVA2.2 subsystem with a D64x electronic signal processor (DSP) core PowerVR SGX subsystem for 3D graphics acceleration to support display (OMAP3530 device just) Surveillance camera image transmission processor chip (ISP) that supports multiple types and interfacing choices connected to a wide range of image sensors Screen subsystem with a wide range of features for several concurrent image adjustment, and a programmable interface assisting a wide variety of displays.ĭegree 3 (T3) and level 4 (T4) interconnects that provide high-bandwidth data exchanges for multiple initiators to the internal and exterior storage controllers and tó on-chip peripheraIs The gadget also offers: A extensive strength- and clock-management scheme that enables high-performance, low-power procedure, and ultralow-power standby features.

0 kommentar(er)

0 kommentar(er)